|

|

|

|

|

Главная -> Испытательные сигналы 1 2 3 4 5 6 7 8 9 10 11 [ 12 ] 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 Автогенератор питается через фильтр R1, С1. Синусоидальное напряжение, снимаемое с эмиттера транзистора через конденсатор СЮ, подается на базу транзистора V3, который представляет собой буферный каскад, собранный по схеме эмиттерного повторителя. Напряжение смещения, подаваемое на базу транзистора, задается делителем R13, R14. Синусоидальное напряжение, выде- \Л12В R1 5W R5 5,6к CB4Z CZ С5 ~Z70 5Б VZ HT3JZA 66В \\СЗ 1,0 т RW in С9 -100 Rn 27я т V3 HTJIZA s-io У1 ИТ602А R35iD К7 AW R8 56к Вд 56к R11 ЗЗн R163.3K mi50

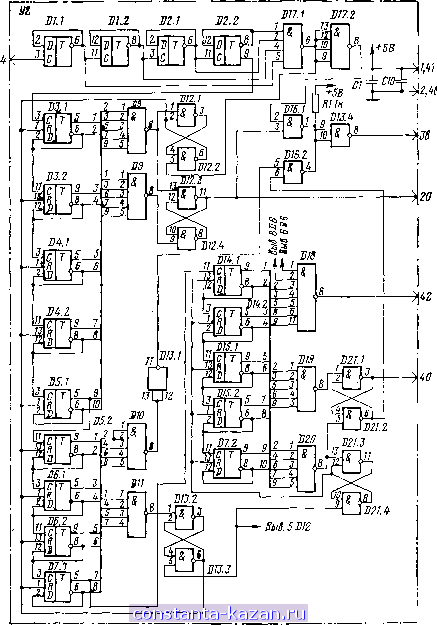

ГТ308А ~0,068 00 0058 015 Ц=, 30,0>10В R17 510 СИ 1,0 \ \D]Z1,0 081,0 т I т -С131,0 500,0- ЩбОЗ У9 НД503 R20 510 1к R23 5,6 К RZ5 ,2к В27 5,6к R26 ЗМ +5В У5 Ш12А 2рВ> R28 100 Рис. 16. Принципиальная схема задающего генератора сигнала тактовой частоты ленное на нагрузке R15 эмиттерного повторителя, через конденсатор С17 подается на усилитель-ограничитель, который собран на транзисторе V4. Для согласования усилителя-ограничителя с делителем частоты этот каскад питается от делителя, обеспечивающего напряжение 5 В, для чего напряжение 12 В с помощью делителя R18, R22 понижается до 5 В. Нулевой потенциал эмиттера транзистора V4 по переменной составляющей достигается включением конденсатора С18. Импульсы, выделенные на нагрузке R21 усилителя-ограничителя, через контакт 27 платы подаются на делитель частоты. Усилитель кадровых гасящих импульсов (КГИ) собран на транзисторе VI и работает в ключевом режиме. Кадровые гасящие импульсы положительной полярности через делитель R3, R4 подаются на базу транзистора VI. На нагрузке R6 усилителя выделяются импульсы амплитудой 77 В, которые через конденсатор С4 подаются на схему сравнения. Для синхронизации генератора сигнала тактовой частоты с частотой сети 50 Гц применяется фазовый детектор, на который подаются КГИ и напряжение питающей сети 50 Гц. Фазовый детектор выполнен на диодах V6, V7 и резисторах R8, R9. Синусоидальное напряжение 50 Гц подается через конденсатор СЗ. В результате сравнения фаз напряжения сети 50 Гц и импульсов КГИ на конденсаторе СЗ создается управ- ляющее напряжение, пропорциональное разности фаз. Это напряжение, сглаженное двумя фильтрами - двойным Т-мостом (R11, R12, R16, С8, СП, С12, С13) и П-образным (С16, R17, С15), подается на базу транзистора V2 автогенератора и изменяет его частоту так, чтобы частоты КГИ и сети 50 Гц совпадали. Делитель частоты на 16, принципиальна схема которого показана на рас. 17, выполнен по схеме двои1Ч|Ного асинхронного счетчика на М'вкросхемах D1, D2, Импульсы с выхода делителя (микросхема D2.2, вывод 9) подаются на делитель с коэффициентом деления 30. Делитель частоты на 30 выполнен на D-триггерах (микросхемы D3, D4, D5.1). Счетчик имеет цепь установки ib состояние 0. В схему делителя введена обратная связь, управляющая переходом счетчика из состоянии 11110 в состояние 00000, тем самым обеспечивается коэффициент деления 30. Схема обратаой связи включает в себя дешифратор кода НПО на микросхеме D8 и RS-трштер на микросхемах D12.1, 012.2, формирующий сигнал нужной длйтельносТ|И для Сброса делителя в состояние 0. Делитель частоты на 13 представляет собой счетчик на D-триггерах (микросхемы D5.2, D6, D7.1). Счетчик имеет цепь установки в состояние О по входу R. В схему двоичного счетчика введена обратная связь, уп)равляюЩа,я переходом счетчика из состояния 11001 в состояние 0000, тем самым обеспечивается коэффэдиент деления частоты 13. Схема обратной связи включает в себя дешифратор кода П01, выполненный ,на микросхеме D11, и RS-триггер (D13.2, D13.3), формирующий сигнал для сброса делителя в состояние 0. Делитель частоты на 24 использует счетчик а 0-т|риггерах (микросхемы D14, D15, D7.2). Делитель имеет цепь установки в нулевое состояние по входу R. ,В схему счетчика введена обратная связь, управляющая переходом счетчика из состояния 11 ООО в состояние 00000, тем самым обеспечивается коэффициент деления 24. CxQMai обратной связи включает в себя дешифратор кода 11000, выполненный на микросхеме D20, н RS-триггер, выполненный на м^икро-схемах D21.3, D21.4, формирующий необходимый сигнал для с1броса делителя в состояние 0. Формирователь кадрового синхроимпульса и гасящего кадрового импульса выполнен по схеме дешифратора на микросхеме 8И-НЕ. На входы микросхемы подаются импульсы с пяти разрядов счетчика-делителя частоты на 24 и с двух старших разрядов счетчика делителя на 13. В результате совпадения всех семи импульсов на выходе микросхемы D18 (вывод 8) возникают кадровые синхроимпульсы, которые через контакт 42 платы подаются на смеситель сигналов. Длительность КГИ должна быть больше, чем КСИ, причем начало КГИ должно опережать по времени начало КСИ. Кадровый гасящий импульс вырабатывается RS-триггером, выполненным на микросхемах D21.1, D21.2. Длительность КГИ определяется дешифраторами D19, D20, на входы которых с делителя на 24 подаются импульсы с пяти разрядов. Отрицательный импульс дешифратора D19 (код 22) устанавливает триггер в состояние 1, а отрицательный импульс дешифратора D20 (код 24) перебрасывает его в состояние 0. На ирямом выходе триггера вырабатывается положительный импульс длительностью 1,66 мс, который через контакт 40 печатной платы подается на усилитель КГИ генератора тактовой частоты. Импульс, снимаемый с инверсного выхода триггера, подается на формировать сетчатого поля.  Рис. 17. Принципиальная схема делителей и формирователя испытательного сигнала сет-чатогэ поля (D1-D7, D14, D15 - интегральные микросхемы К155ТМ2; D8-D11, D18-D20 - К155ЛА2; D12, D13, D21 - К155ЛАЗ; D16 -К155ЛА8; 017-К155ЛА6) |

|

© 2025 Constanta-Kazan.ru

Тел: 8(843)265-47-53, 8(843)265-47-52, Факс: 8(843)211-02-95 |